## Article

# A Hybridization of Cuk and Boost Converter Using Single Switch with Higher Voltage Gain Compatibility

M. Karthikeyan <sup>1,\*</sup>, R. Elavarasu <sup>2</sup>, P. Ramesh <sup>3</sup>, C. Bharatiraja <sup>4</sup>, P. Sanjeevikumar <sup>5</sup>, Lucian Mihet-Popa <sup>6,\*</sup> and Massimo Mitolo <sup>7</sup>

- <sup>1</sup> Department of Electrical and Electronics Engineering, University College of Engineering, Pattukkottai 614701, Tamilnadu, India

- <sup>2</sup> Department of Electrical and Electronics Engineering, Rajalakshmi Institute of Technology, Chennai 600124, Tamilnadu, India; elava3000@gmail.com

- <sup>3</sup> Department of Electrical and Electronics Engineering, CMR Institute of Technology, Bengaluru 560037, India; ramesh8889@gmail.com

- <sup>4</sup> Department of Electrical and Electronics Engineering, SRM Institute of Science and Technology, Chennai 603 203, India; bharatiraja@gmail.com

- <sup>5</sup> Department of Energy Technology, Aalborg University, 6700 Esbjerg, Denmark; san@et.aau.dk

- <sup>6</sup> Faculty of Engineering, Østfold University College, Kobberslagerstredet 5, 1671 Kråkeroy-Fredrikstad, Norway; lucian.mihet@hiof.no

- <sup>7</sup> School of Integrated Design, Engineering and Automation Irvine Valley College, Irvine, CA 92618, USA; mmitolo@ivc.edu

- \* Correspondence: kar\_thamarai82@yahoo.com; lucian.mihet@hiof.no

Received: 31 March 2020; Accepted: 27 April 2020; Published: 6 May 2020

Abstract: In the current era, the desire for high boost DC-to-DC converter development has increased. Notably, there has been voltage gain improvement without adding extra power switches, and a large number of passive components have advanced. Magnetically coupled isolated converters are suggested for the higher voltage gain. These converters use large size inductors, and thus the non-isolated traditional boost, Cuk and Sepic converters are modified to increase their gain by adding an extra switch, inductors and capacitors. These converters increase circuit complexity and become bulky. In this paper, we present a hybrid high voltage gain nonisolated single switch converter for photovoltaic applications. The proposed converter connects the standard conventional Cuk and boost converter in parallel for providing continuous current mode operation with the help of a single power switch, which gives less voltage stress on controlled switch and diodes. The proposed hybrid topology uses a single switch with a lower componentcount and provides a higher voltage gain than non-isolated traditional converters. The converter circuit mode of operation, operating performance, mathematical derivations and steady-state exploration and circuit parameters design procedures are deliberated in detail. The proposed hybrid converter circuit components, voltage gain and performance, were compared with other topologies in the literature. The MATLAB/Simulink simulation study and microcontroller-based experimental laboratory prototype of 150 W were implemented. The simulation study and experimentation results were confirmed to be a satisfactory agreement with the theoretical analysis. This topology produced non-inverting output in continuous input current mode using a single switch with high voltage gain ( $\approx$ 5.116 gain) with a maximum efficiency of 92.2% under full load.

**Keywords:** DC-to-DC converter; single switch high voltage gain converter; non-isolated DC-to-DC converter; low voltage stress; higher voltage gain

## 1. Introduction

Due to the increase in energy demand, large amounts of conventional energy have been consumed, which is very dangerous due to their CO2 emissions. For example, all countries are keen on replacing conventional energy sources with non-conventional sources. Researchers are currently exploring power converters and interfacing circuits to meet out-migration. Non-conventional sources such as wind energy [1,2], photovoltaic (PV) [3,4] and hydrogen-powered fuel cells (FC) [5,6] are leading sources for meeting commercial and industrial demands. A PV-powered power system consists of PV modules coupled in a series as well as parallel combinations that are fed to the required DC voltage through the DC-to-DC converter, which is then converted as a DC-to-AC source through the inverter [7]. The controller development of DC-to-DC converters using a fuzzy logic controller and sliding mode control has recently gained attention. Those converters are used in a microgrid that minimizes the instability effects in [8] and [9]. For optimizing the performance of the converter, an optimization algorithm was used to tune the controller's coefficients [9]. A constant power load in a shipboard DC microgrid was investigated for the finite time by adopting the finitetime disturbance observer method [10]. The estimated load power was then received by the fixedtime terminal sliding mode controller to stabilize the entire marine power grid as well as tracking the reference voltage of the DC bus in a fixed time independent of initial conditions. For a highefficiency PV system, a dual-power stage micro-inverter (high voltage gain DC-to-DC converter + DC-to-AC inverter) was issued in the market. In many industrial applications such as those found in the automotive, telecommunication and shipping industries, systems need higher voltage gain DCto-DC converters with large input current [11–13]. These converters typically boost the range from 24–60 V to 100–300 V. For example, automotive headlamps need 48/100/120 V range, but the vehicle battery capacity can only deliver 12/24/48 V. For these situations, high voltage converters are suggested with high voltage gain [14,15]. According to the theoretical calculations, the conventional boost converter can offer a high duty ratio with infinite voltage gain. However, in a practical case, it is limited due to the inductor saturation limits. Besides, any DC-to-DC converter, which needs to provide a high output voltage and high power conversion, draws large input current; hence, the power switches metal-oxide-semiconductor field-effect transistor (MOSFET) and diode) are needed to handle the voltage stress.

Topologies have presented numerous single switch converters in the literature to provide the high step-up voltage conversion [14–20]. These converters have some limitations for their voltage gain, which is mainly because of the inductors, power semiconductor switches and the parasitic elements of those converters. Hence, a researcher has recommended using a step-up transformer with a converter to overcome this issue (flyback converter) [21]. It may be achieved with a high current for high power uses, which is not the most efficient. Other attempts have been made by using a single switch with a forward and tapped inductor connected converters are proposed for high voltage gain [22–24]. Though these converters have a controlled degree of freedom through the transformer turns ratio adjustment, considering the transformer size, the converter is large. The high voltage gain quadratic converters are the next choice in this group [25,26]. However, a quadratic converter has high voltage stress across the first semiconductor, resulting in it being more efficient than the classical converter. The impedance (using two inductors and two capacitors) source-based converter handles the buck-boost voltage conversion with high gain; however, it needs a high voltage-handling power switch to operate shoot-through and not shoot-through operation. A high voltage gain integrated boost and flyback converter is proposed by [27] using the leakage inductor energy recirculation in the switch-off period; however, this method suffered from pulsating input currents.

The converter topology accumulated with a coupled inductor produces a high step-up conversion with high efficiency [28,29]. Here, the voltage gain is dealt with by changing the converter switch turns ratio like isolated type converters. Though this topology obtains a high gain, due to the coupled inductor-leakage inductance, the switch may suffer a high voltage spike. The passive and active clamping approaches have been established [30] by adding a coupled inductor for the high voltage conversion ratio; however, this converter is inefficient in terms of cost and size.

The other choice is adapting a switched capacitor in the switching-mode converter for the high voltage gain [28,29]. Due to the pulse shape, the input current of the converter leads to a weak load and line regulation problems. The voltage-doubler concept in converters [30–34] can provide a high voltage gain with the coupled inductor. Here, the switching frequency is less than an inductor magnetizing current frequency, which is not suitable for reliable operation. Recently, using the single switch in DC-to-DC power converters, various research papers have been published to derive high voltage gain without using a higher duty ratio [35–40]. The authors in [33] proposed a 2D/1-D voltage gain single switch buck-boost converter with low input current ripple and appropriate voltage gain. Nevertheless, it has the discontinuous current in the input side. In paper [37], a transformerless high voltage gain buck-boost was proposed with a voltage gain of 3D/1-D; though this converter has a discontinuous input current. A quadratic DC–DC buck–boost converter with single-switch topology is presented in [39] for widespread voltage conversion. The high step-up single switch converter is recommended for PV-based grid applications [30]. However, in this converter, the low-level input voltage habitually roots massive input current and higher current ripples. This large amount of current affects the power switch during the higher duty ratio operation, causing a large conduction loss. Recently, Banaei et al. proposed a converter using a single switch with less switching voltage stress. Even though the converter can maintain the continuous input current for all duty ratios, the primary power switch voltage stress is strictly equal to the converter output voltage, which caused high conduction losses [38]. In [40] and [41], the single switch Cuk topology uses an extra inductor and capacitor to provide the extra voltage. However, in this topology, when diodes are operating with higher current and voltage, the diode reverse recovery current is predominant, which increases the switching losses. Among all converter topology, the cascade boost converter type is proficient in obtaining a higher gain with minimal duty ratio for the full range of voltage gain [19]. Nevertheless, the main switch has higher voltage stress in this topology.

Based on this discussion, and although several single switch boost converter topologies are proposed in the literature, their major approaches are concerned with the use of less magnetic elements, size, weight, conduction losses and cost-savings for the inductors. These approaches have higher voltage stresses on their switch (nearly the same as their output voltage). Therefore, these converters still have significant challenges, such as high step-up requirements for the larger duty ratio, output diode reverse recovery complication, higher switching voltage stress and satisfactory efficiency. Integrating the classical DC-to-DC converter is a better choice than modifying an existing converter. However, while cascading those classical converters with additional boosting capability, reducing the power switches and passive elements leads to an appropriate converter circuit size as well as cost reductions. With that aim, in this paper, we propose a DC–DC converter topology by integrating the conventional boost and Cuk converters with high voltage gain. Our proposed topology uses only one power switch with higher static voltage gain when compared to other conventional converters. Our proposed converter delivers voltage using two series-connected identical capacitors connected in parallel with the converter circuit. In this paper, we also deal with the maintenance of the capacitor balancing. The detailed converter mode operation, analysis, design, small-signal analysis and analytical switching losses were deliberated. The MATLAB/Simulink simulation and PIC microcontroller-based experimentation results for the integrated converter shows the advantages and practicality of the proposed converter.

The paper is organized as follows: Section 2 describes the proposed hybrid converter design and its mode of operation. Section 3 describes the converter components design and small-signal analysis. Section 4 explains the design procedure and components. The simulation, experimentation and comparison with other similar topologies are discussed in Sections 5 and 6. The conclusion is given at the end of Section 7.

#### 2. Topology and Operation of Proposed Hybrid DC-DC Converter

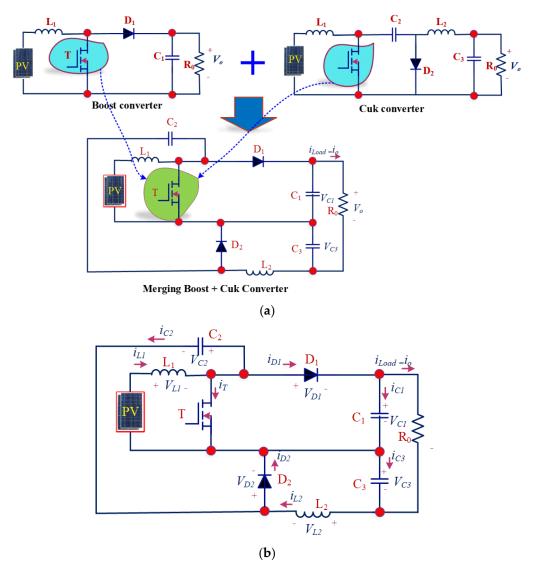

The proposed integrated hybrid converter combines the conventional boost converter and classical Cuk DC-to-DC converter. The method used for the design of the proposed hybrid converter

topology is illustrated in Figure 1. Figure 1a,b shows the typical conventional boost converter and classical Cuk converter, respectively. In both of these converters, the input inductor, power switches and input source are organized in the same way. Hence, there is an opportunity to merge these two converters by keeping the power switch and input inductor commonly on the input side. Except for the input side boost inductor (L<sub>1</sub>) and the power switch T, the rest of the circuit is connected precisely in parallel with each other. Hence, the output side two capacitors (C<sub>1</sub> and C<sub>3</sub>) are placed across the load. This hybrid structure increases the voltage gain by complementing the benefits of boost and Cuk converters. The converter provides continuous current mode operation with the help of a single power switch, which provides less voltage stress on the controlled switch and diodes.

Figure 1. (a) Proposed converter integration; (b) proposed single switch hybrid DC–DC converter.

## Operation of Hybrid DC–DC Converter

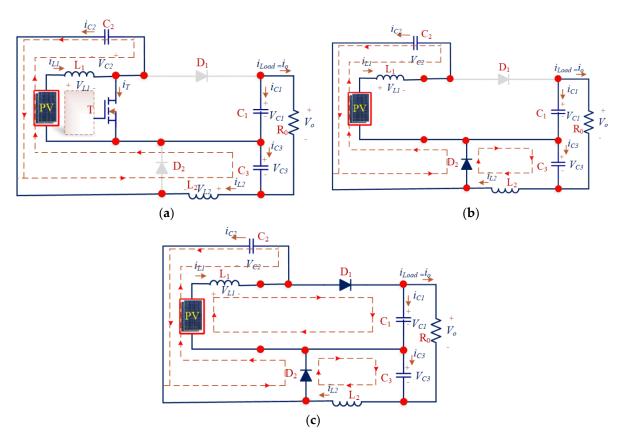

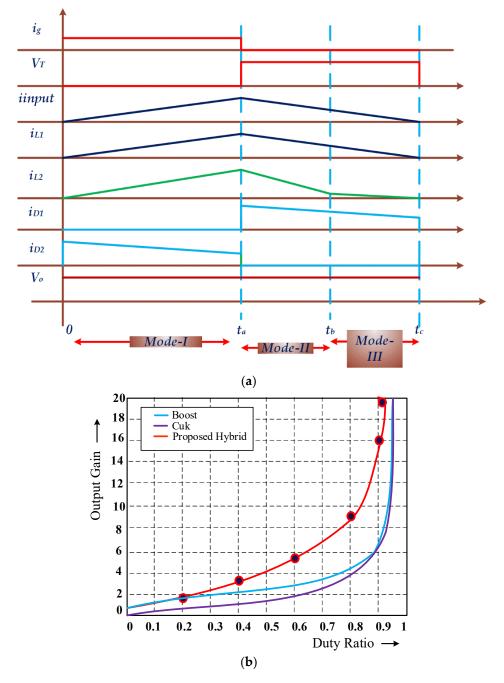

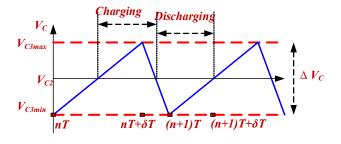

The proposed hybrid DC–DC converter mode operations, their capacitors (C<sub>1</sub>, C<sub>2</sub> and C<sub>3</sub>) and inductors (L<sub>1</sub> and L<sub>2</sub>) charging and discharging analysis derivations were considered as follows. The two assumptions were taken for this analysis: (1) all the components are ideal; (2) the converter works under continuous conduction. Figure 3a illustrates the continuous conduction operating mode waveforms of the proposed converter. This advanced hybrid DC–DC converter mode operation has three modes of operation.

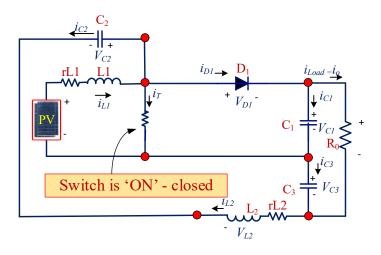

• Mode- I [t<sub>a</sub>-t<sub>b</sub>], presented in Figure 2a. During mode-1, when t = t<sub>a</sub>, the power switch T is turned ON and inductors (L<sub>1</sub> and L<sub>2</sub>) are charging until t<sub>b</sub>. In the same interval, the capacitor C<sub>2</sub> is

discharging through T, and inductor  $L_2$  as the diodes (D<sub>1</sub> and D<sub>2</sub>) are blocking concerning V<sub>C1</sub> and V<sub>C2</sub>.

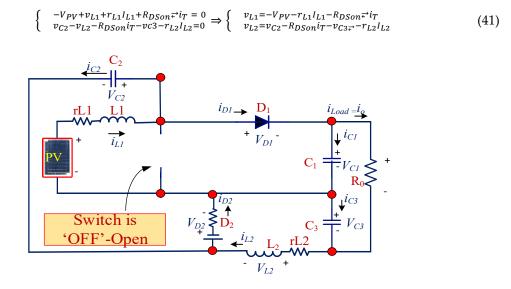

- Mode- II [tb-tc], illustrated in Figure 2b. During mode-1, when t = tb, the power switch T is in the OFF state. Now the capacitor C1 voltage (Vc1) is higher than Vc2. Hence, after tb interval, the C2 is charging and inductors L1 and L2 are discharging. It is happening throughout tb to tc. In the course of this period, diode D2 is continuously conducting since diode D1 is still in reverse bias.

- Mode- III [t-td], presented in Figure 2c. During this mode, the power switch T remains OFF as well as the Vc1 is equal or lesser than Vc2. Here, both the inductors L1 and L2 are discharging, and C1 and C2 are charging via L1. Hence the diode D1 and D2 are conducting and delivering the current to load.

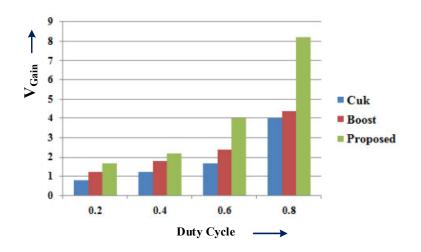

The proposed hybrid DC-to-DC converter operation mode waveforms are presented in Figure 3. In mode-I, the power switch T is 'ON' and turned 'OFF' in mode-II as well as mode-III. The proposed converter duty ratio versus voltage gain performance was compared to boost and Cuk converters. Figure 3b displays the voltage gain versus duty ratios for boost, Cuk and the proposed hybrid converter. Based on the plot, it can be seen that the proposed hybrid converter has a better voltage gain ratio when compared with the boost and Cuk converter, respectively. In addition to the extended voltage static gain, the proposed topology achieves lower voltage stress across the power switch and diodes, when compared to a boost converter.

The power switch voltage stress is equal to the peak voltage across the capacitor C1. Hence, voltage stress across the power switch T was lower than the total output voltage. The voltage stress of D1 and D2 is equal to the voltage across the power switch T in the OFF state. Hence, the diodes' current rating requirement was lower than power switch T. In the classical boost converters for both Cuk and boost, the power switch and diode need an equal rating. In the higher gain operations, the classical converter needs a higher duty cycle than the proposed converter. Therefore, the voltage stress for switch and diode are higher. Hence, the proposed converter efficiency in the higher gain operation is better than the conventional boost converter.

**Figure 2.** Modes of operation of the proposed hybrid DC-to-DC converter: (**a**) Mode- I [t<sub>a</sub>-t<sub>b</sub>]; (**b**) Mode- II [t<sub>b</sub>-t<sub>c</sub>]; (**c**) Mode- III [t<sub>c</sub>-t<sub>d</sub>].

**Figure 3.** (a) Mode diagram of the proposed circuit; (b) voltage gain versus duty ratio for boost, Cuk and proposed hybrid converter.

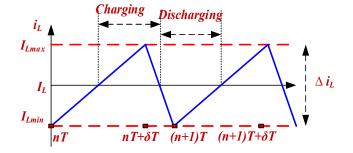

In general, for any DC-to-DC converter, the input inductor selection is carried out depending on the converter conduction mode, load current requirement, and it is desirable to confirm the least output current ripple. Hence, the input inductor L<sub>1</sub> value was chosen with minimal current ripple  $\Delta_{iL}$ . The inductor current, iL for the proposed converter is supplied from either a PV or DC source (V<sub>PV</sub> or V<sub>in</sub>). When the converter receives a supply voltage from the input source, the converter power switch T is turned ON, and inductor current iL<sub>1</sub> is derived as follows. Applying Kirchhoff's voltage law in mode-I [t<sub>a</sub>-t<sub>b</sub>], the capacitors current ic<sub>1</sub> and ic<sub>2</sub> are derived as

$$-V_{PV} + v_{L1} = 0 \Rightarrow v_{L1} = V_{PV} \tag{1}$$

$$-v_{C2} + v_{L2} + v_{C3} = 0 \Rightarrow v_{L2} = -v_{C3} + v_{C2}$$

$$-i_T + i_{L1} - i_{C2} = 0 (2)$$

$$i_{0} - i_{L2} - i_{C3} = 0$$

$$i_{C2} = -i_{L2}$$

$$i_{C1} = -i_{0}$$

(3)

During mode-II [ $t_b-t_c$ ], when the power switch T is in OFF, the coil transfers energy to the capacitors C<sub>1</sub> and C<sub>3</sub>. As a result, from loop 1 and loop 2, it can verify that

$$-V_{PV} + v_{L1} + v_{C2} = 0 \Rightarrow v_{L1} = -v_{C2} + V_{PV}$$

$$v_{L2} + v_{C3} = 0 \Rightarrow v_{L2} = -v_{C3}$$

$$v_{C2} = v_{C1}$$

(4)

From loop 1 and loop 2 (mode-II Figure 2b), the capacitor current ic1 and ic2 are derived as follows,

$$i_{C1} = i_{D1} - i_0 \tag{5}$$

$$i_{C2} = i_{L1} - i_{D1} = i_{D2} - i_{L2}$$

$$I_C = \frac{1}{T} \int_0^T i_C dt = \frac{C}{T} \int_0^T dv_C (t) = \frac{C}{T} \left( v_C(T) - v_C(0) \right)$$

(6)

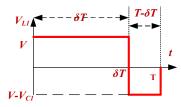

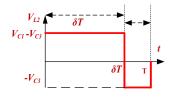

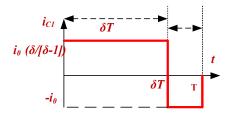

during steady-state condition  $V_{C(T)} = V_{C(0)}$ . Hence, the average value of the current capacitors is null. Also, the inductor coils average voltage is zero, since  $v_L(t) = L \frac{di_L(t)}{dt}$ . The currents in the inductors and voltage in the capacitors tend to be approximately constant. The power switch is in the ON state for a percentage of the period ( $\delta$ T) and OFF during the next state ( $\delta$ T-T). Here, T is the total switching time. Therefore, the average value inductor voltage V<sub>L1</sub> and capacitor's current ic<sub>1</sub> are illustrated in Figures 4 and 7.

Figure 4. Inductor voltage VL1.

$$V_{L1} = \frac{1}{T} \left[ \int_{0}^{\delta T} V_{PV} dt + \int_{\delta T}^{T} (V_{PV} - V_{C1}) dt \right] = 0$$

(7)

Replacing the voltage on the calculation, we obtain the capacitor voltage Vc1

$$V_{C1} = \frac{1}{1 - \delta} V_{PV} \tag{8}$$

The inductor L<sub>2</sub> voltage is illustrated in Figure 5, and inductor average voltage value is

Figure 5. Inductor voltage VL2.

$$V_{L2} = \frac{1}{T} \left[ \int_0^{\delta T} (V_{C1} - V_{C3}) dt + \int_{\delta T}^T - V_{C3} dt \right] = 0$$

(9)

The voltage across the capacitor C<sub>3</sub> can be written as

$$V_{C3} = \frac{\delta}{1 - \delta} V_{PV} \tag{10}$$

Hence, the converter output voltage can be calculated as

$$V_O = \frac{1+\delta}{1-\delta} V_{PV} \tag{11}$$

By equating the converter input power and output power, the input inductor current is derived as

$$V_{PV}I_{L1} = V_OI_O \Rightarrow I_{L1} = \frac{1+\delta}{1-\delta}I_O$$

(12)

When the Kirchhoff's current law is applied in the loop

$$i_{C3} + i_0 - i_{L2} = 0 \Rightarrow i_{L2} = i_{C3} + i_0 \tag{13}$$

The capacitor C<sub>3</sub> charge and discharge current is shown in Figure 6. Here the capacitor current average value observed is zero, and the average current in the inductor is similar to the average output current, as the inductor tends to retain that average value.

Figure 6. Capacitor current ic3.

Assuming that i0= i12

Figure 7. Capacitor current C1.

The mean value of the capacitor C<sub>1</sub> current (ic<sub>1</sub>) is displayed in Figure 7. From the capacitor current interval zero to  $\delta T$  and  $\delta$  to T time, the ic<sub>1</sub> is calculated as

$$I_{C1} = \frac{1}{T} \left[ \int_0^{\delta T} (-i_0) dt + \int_{\delta T}^T (i_{D1} - i_0) dt \right] = 0$$

(14)

$$i_{D1} - i_0 = i_0 \frac{\delta}{1 - \delta} \tag{15}$$

When the power switch T is turned ON, the diode D1 current is calculated as

$$i_{D1} = \frac{I_0}{1 - \delta} \tag{16}$$

Similarly, when the power switch T is turned OFF, the diode D2 current is calculated as

$$i_{L1} - i_{D1} = i_{D2} - i_{L2} = I_0 \frac{\delta}{1 - \delta}$$

(17)

$$i_{D2} = \frac{I_0}{1 - \delta} \tag{18}$$

The current of the power switch T can be written as

$$i_T = i_{L1} - i_{C2} = \frac{2I_0}{1 - \delta} \tag{19}$$

#### 3. Scaling Converter Components Design

The proposed hybrid converter reactive components, inductors coil ( $L_1$  and  $L_2$ ) and capacitors ( $C_1$ ,  $C_2$  and  $C_3$ ), are calculated for maximum values as the power switch T should support both the converter voltage and current.

## 3.1. Design of Inductors

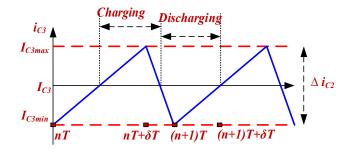

The inductor coil ( $L_1$  and  $L_2$ ) values calculation and current limitation analysis are observed by precise variation concerning the average value shown in Figure 8. The differential equation of inductor voltage V<sub>L</sub> is shown as

$$v_L(t) = L \frac{di_L(t)}{dt}$$

(20)

Figure 8. Evolution of the inductor current.

By assuming inductor voltage  $V_L$  nearly constant, the current equation inductor is calculated as follows

$$i_L(t) = \frac{v_L}{L} \Delta t_L + i_L(t0)$$

<sup>(21)</sup>

Thus,  $v_L(t) = L \frac{di_L(t)}{dt}$  it becomes

$$\frac{\Delta i_L}{\Delta t_L} = \frac{\nu_L}{L} \tag{22}$$

Using the instantaneous inductor voltage equation, the inductor voltage will be

$$v_{L1} = \begin{cases} v_{PV}, & nT < t < nT + \delta T \\ v_{PV} - V_{C1}, nT + \delta T < t < (n+1)T \end{cases}$$

(23)

During 'ON' state of the power switch,  $\Delta t_L = \delta T$

$$L_1 = \frac{V_{PV}\delta T}{\Delta i_{L1}} \tag{10}$$

$$v_{L2} = \begin{cases} v_{C1-v_{C3,}} & nT < t < nT + \delta T \\ -v_{C3,} & nT + \delta T < t < (n+1)T \end{cases}$$

(25)

For the 'OFF' state of the power switch, it has  $\Delta t_L = (1 - \delta)T$

$$L_{2} = \frac{\nu_{C3}(1-\delta)T}{\Delta i_{L2}}$$

(26)

# 3.2. Design of Capacitors

The calculation of capacitor values  $C_1$ ,  $C_2$  and  $C_3$  are given below. The changing and discharging variation around the average value is shown in Figure 9.

Figure 9. Evolution of the current in the coil.

The differential equation of the capacitor

$$i_c(t) = C \frac{dv_c(t)}{dt}$$

<sup>(27)</sup>

Similar to the calculation of inductors, the capacitor variation is calculated using Equation (27) after linearization of  $i_c(t) = C \frac{dv_c(t)}{dt}$  becomes,

$$\frac{\Delta v_c}{\Delta t_c} = \frac{i_c}{C} \tag{28}$$

With the instantaneous value of the capacitor current over a certain period, the value of the capacitor can be calculated. For capacitor C<sub>1</sub>, the current is given by:

$$i_{C1} = \begin{cases} -I_0, & nT < t_{\vec{r}} < nT + \delta T \\ I_0 \frac{\delta}{1 - \delta'}, & nT + \delta T < t < (n+1)T \end{cases}$$

(29)

During the first-time interval, for  $\Delta t_c = \delta T$ ,  $C_1$  is

$$C_1 = \frac{I_0 \delta T}{\Delta v_{C1}} \tag{30}$$

The capacitor current  $C_2$  is given by

$$i_{C2} = \begin{cases} -I_{0,} & nT < t_{\overline{\tau}} < nT + \delta T \\ I_0 \frac{\delta}{1 - \delta}, & nT + \delta T < t < (n+1)T \end{cases}$$

(31)

During the time interval, when  $\Delta t_c = \delta T$

$$C_2 = \frac{I_0 \delta T}{\Delta v_{C2}} \tag{32}$$

For capacitor  $C_3$ , the current does not show instantaneous values and is nearly constant during the switching state. The behavior of capacitor  $C_3$  is opposite capacitors  $C_1$  and  $C_2$ . When controlling the power semiconductor switch for the driving load variation, capacitor charge  $\Delta Q$  is related to the inductor current  $\Delta i L_2/2$  and time is taken T/2.

$$Q = Cv_c \Rightarrow C = \frac{Q}{v_c'} \quad C_3 = \frac{\Delta Q}{\Delta v_{c3}}$$

(33)

At load variation,

$$\Delta Q = \frac{\frac{T\Delta i_2}{2}}{2} = \frac{T\Delta i_{L2}}{8}$$

(34)

The capacitor  $C_3$  value is calculated as  $C_3 = \frac{T\Delta i_{L2}}{8\Delta v_{c3}}$  (35)

In the dynamic condition, capacitors  $C_1$  and  $C_3$  values are deliberate in this section. The calculation is computed by including the sudden change in drive load resistance. Output voltage in the dynamic operating region is determined using the equivalent circuit (Figures 10 and 11), assuming that the current passes zero to its steady-state value,  $\Delta t_1$ , the settling time of the current in the inductor  $L_1$ .

$$i_{C1} = C_1 \frac{dv_{C1}}{dt} = -i_0 \quad \Rightarrow v_{C1}(t) = \frac{1}{C_1} \int_0^t (-i_0) dt + v_{C1}(0)$$

(36)

$$v_{C1}(\Delta t_1) = \frac{1}{C_1} \int_0^t (-i_0) dt + v_{C1}(0) = -\frac{1}{C_1} \frac{P_0}{V_0} \Delta t_1 + v_{C1}(0)$$

(37)

Thus, capacitor voltage VC1 is calculated using Equation (37)

$$v_{C1}(\Delta t_1) = \frac{1}{C_1} \int_0^t (-i_0) dt + v_{C1}(0) = \frac{1}{C_1} \frac{P_0}{V_0} \Delta t_1 \Rightarrow C_{-1} = \frac{1}{\Delta v_{C1}} \frac{P_0}{V_0}$$

(38)

In a dynamic case, while changing the converter duty ratio, the inductor current increases coil rapidly. Hence, the  $\Delta t_1$  value needs to calculate, in detail, from the response of  $i_{L1}(s)$ , which displays the input current of the response when rapid changes occur in output current  $i_0(s)$ . At time  $\Delta_{12}$ , the current flow through the capacitor  $C_3$  is calculated as

$$i_{C3} = C_2 \frac{dv_{C3}}{dt} = -i_0 \tag{39}$$

$$C_3 = \frac{1}{\Delta v_{C3}} \frac{P_0}{V_0} \Delta t_2$$

(40)

For calculation straightforwardness, it is assumed that the current has equal settling times.

In terms of the energetic properties, the proposal converter is similar to the boost and Cuk converters. The proposed converter input inductor, power switches and input source are organized the same way as the classical boost and Cuk converters. Except for the input side boost inductor (L<sub>1</sub>) and the power switch T, the rest of the proposed converter circuit elements are connected precisely in parallel with each other and on the output side, two capacitors (C<sub>1</sub> and C<sub>3</sub>) are placed across the load. Therefore, the proposed converter increases the voltage gain by combining the benefits of boost and Cuk converters.

#### 3.3. Small Signal Analysis of Hybrid DC–DC Converter

The average equivalent circuit model of the proposed hybrid DC–DC converter was derived and is presented in Figure 10. The circuit analysis was derived for the switch in both the ON and OFF period. The initial conditions were an approach to obtain the average value of the coil; the current remained the same.

Figure 10. Equivalent circuit of the converter with losses in the mode-1 operation.

By the application of mesh law to the circuit in Figure 10, we can verify that

Figure 11. Equivalent circuit of the converter with losses in mode-2 and mode-3 operation.

$$\begin{cases} -V_{PV} + v_{L1} + r_{L1}I_{L1} + v_{C2} + V_{D2} + R_{D2}\vec{\tau} i_{D2} = 0 \\ v_{L2} + r_{L2}I_{L2} + v_{C3} + V_{D2} + R_{D2}i_{D2} = 0 \end{cases} \Rightarrow \begin{cases} v_{L1} = -V_{PV} - r_{L1}I_{L1} - v_{C2} - V_{D2} - R_{DSon}\vec{\tau} i_T \\ v_{L2} = -r_{L2}I_{L2} - v_{C3} - V_{D2} - R_{D2}i_{D2} \end{cases}$$

(42)

$$-V_{PV} + v_{L1} + r_{L1}I_{L1} + v_{C1} + v_{D1} + R_{D1}i_{D1} = 0$$

(43)

$v_{D1} = v_{D2}, R_{D1}i_{D1} = R_{D2}i_{D2}, v_{C2} = v_{C1}$ From the waveform  $v_{L1}$  and  $v_{L2}$ ,

$$V_{L1A} = V_{PV} - R_{Dson} I_T - r_{L1} I_{L1}$$

(44)

$$V_{L1B} = V_{PV} - r_{L1}I_{L1} - V_{C1} - V_{D2} - R_{D2}I_{D2}$$

(45)

$$V_{L2A} = V_{C1} - R_{DSON}I_{SC} - V_{C3} - r_{L2}I_{L2}$$

(46)

$$V_{L2B} = -r_{L2}I_{L2} - V_{C3} - V_{D2} - R_{D2}I_{D2}$$

(47)

The analysis of converter input to output relation is calculated with losses and approximated with ideal semiconductor devices. The output voltage expressions of the converter were derived and are given below.

$$V_{L1} = 0 \Rightarrow V_{C1} = \frac{V_{PV} - r_{L1}I_{L1}}{1 - \delta}$$

(48)

$$V_{L2} = 0 \Rightarrow V_{C3} = \frac{\delta}{1 - \delta} (V_{PV} - r_{L1}I_{L1}) - r_{L2}I_{L2}$$

(49)

From the expressions Vc1 and Vc2, the voltage gain converter is calculated as

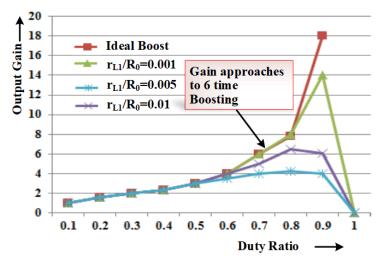

$$\frac{V_0}{V_{PV}} = \frac{1+\delta}{1-\delta + \frac{r_{L1}}{R_0} \frac{(1+\delta)^2}{1-\delta} + \frac{r_{L2}}{R_0} (1-\delta)}$$

(50)

where  $r_{L1}/R_0 = r_{L2}/R_0$ .

Figure 12 illustrates the voltage output gain versus the duty cycle for the proposed hybrid converter. The Figure indicates the ideal condition ( $r_{L1}/R_0=0$ ), where losses need to be introduced in the circuit (the gain for unit value goes to zero, as expected) and other operating conditions  $r_{L1}/R_0 = r_{L2}/R_0 = 0.0001$  to 0.76, where near 0.76 duty cycle, the converter gain approaches six times boosting ( $V_0=6V_{in}$ ).

Figure 12. Voltage output gain versus duty cycle.

## 3.4. Analysis of Losses

The losses of each indictor L<sub>1</sub> and L<sub>2</sub> are denoted from internal resistors  $r_{L1}$  and  $r_{L2}$ , respectively. Thus, the losses in  $r_{L1}$

$$P_{\vec{\epsilon}}r_{L1} = p_1 \vec{\epsilon} P_i \vec{\epsilon} = r_{L1}I_{L1rms^2} \Leftrightarrow r_{L1} = \frac{p_1 P_i}{I_{L1rms^2}}$$

(51)

The sufficient value is given as

$$I_{L1rms} = \sqrt{I_{L1}^{2} + \left(\frac{\Delta i_{L1}}{2\sqrt{3}}\right)^{2}} = \sqrt{I_{L1}^{2} + \left(\frac{0.1I_{L1}}{2\sqrt{3}}\right)^{2}} = I_{L1}\sqrt{1 + \left(\frac{0.1}{2\sqrt{3}}\right)^{2}}$$

$$\Delta i_{L2} = 0.1I_{L2}$$

(52)

Since both the inductors are identical,  $\Delta i_{L1} = 0.1 I_{L1}$  (53) Two kinds of losses in the semiconductor are driving and switching.

#### 3.5. Conduction Losses in the Diodes

The losses in the diode are given as

$$P_D = \frac{1}{T} \int_0^T v_D(t) \, i_D(t) dt = V_D I_D + R_D I_{Drms}^2 \tag{54}$$

$$v_D(t) = V_D + R_D i_D(t) \tag{55}$$

Specific to the case of the diode, for mode-2 operation:

$$i_{D1}(\delta T < t < T) = \frac{I_0}{(1-\delta)}$$

(11)

$$I_{D1} = \frac{1}{T} \int_0^T i_{ak1}(t) \, dt = I_0 \tag{12}$$

$$I_{D1rms} = \sqrt{\frac{1}{T} \int_{0}^{T} i_{D1}^{2}(t) dt} = \frac{I_{0}}{\sqrt{(1-\delta)}}$$

(58)

Thus, resistance is calculated as

$$P_{D1} = \frac{p_3}{2} P_i = V_{D1} I_0 + R_{D1} \left( \frac{I_0}{\sqrt{(1-\delta)}} \right)^2 \Leftrightarrow R_{D1} = \left( \frac{p_3}{2} P_i - V_{D1} I_0 \right) \frac{(1-\delta)}{I_0^2}$$

(59)

The same can be applied to D<sub>2</sub>, resulting in the same results for this diode

$$R_{D2} = \left(\frac{p_3}{2}P_i - V_{D2}I_0\right)\frac{(1-\delta)}{I_0^2}$$

(60)

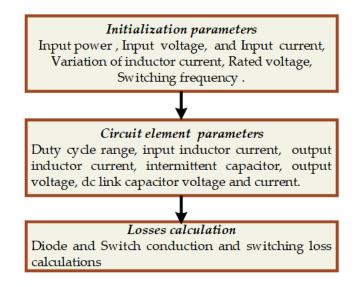

#### 4. Design Procedure

The component selections and other design parameters of the proposed converter at the power range of 150 W were calculated and are presented. The input power was considered a DC-fixed source. The general diagram of the converter design flow chart is shown in Figure 13.

Figure 13. Design setup of converter parameter selections.

To illustrate the numerical values of converters, capacitor and inductors, the below parameters were fixed for the converter design.

- i. The input power  $P_{in} = 150$  W, for  $V_{in} = 24$  V,  $I_{in} = 6.2$  A;

- ii. Power of the converter, P<sub>i</sub> = 150 W;

- iii. Input voltage converter  $V_{in} = 24 \text{ V}$ ;

- iv. Duty cycle is fixed as  $\delta = 0.8$ ;

- v. The converter output voltage,  $V_0 = 104$  V;

- vi. The output current and inductor current were expected to be  $I_0 = 1.11$  A and  $I_{L1} = 4.25$  A, respectively;

- vii. The capacitor  $C_1$  and  $C_3$  voltages were calculated as  $V_{C1} = 110$  V and  $V_{C3} = 104$  V;

- viii. The general typical value sizing of capacitor  $C_1$ ,  $C_3$  and  $L_1$ ,  $L_2$  was calculated as  $\Delta i_{L1} = 10\% I_{L1}$ , hence for  $L_1 = 1$  mH, the change in this was  $\Delta i_{L1} = 0.425$  A. The same changes can be seen for  $\Delta i_{L2} = 10\% I_{L2}$ ,  $L_2 = 1$  mH and  $\Delta i_{L2} = 0.14$  A;

- ix. When the change in the capacitor  $\Delta V_{C1}$  was 1%  $V_{C1}$ , the capacitor  $C_1$  value was 100 µF and  $\Delta V_{C1}$ = 1.10 V. Similarly, for  $\Delta V_{C2}$  = 1%  $V_{C2}$ ,  $C_2$  = 100 µF,  $\Delta V_{C2}$  = 1.04V and  $\Delta V_{C3}$  = 1%  $V_{C3}$ ,  $C_3$  = 2 µF,  $\Delta V_{C3}$  = 0.08 V;

- x. For the power semiconductor switch, the maximum open-circuit voltage was  $V_{Smax} = 100 \text{ V}$ ,  $V_{Smax} = 95 \text{ V}$ ;

- xi. Diodes  $D_1$  and  $D_2$ ,  $V_{Smax} = 100$  V,  $V_{Smax} = 95$  V.

The  $D_1$  and  $D_2$  can ensure a voltage of 100V, which ensures the safety factor of the converter. The converter can support a maximum current of six amps. When using six amps, the current safety factor is reduced to 60%–65%. Hence, the semiconductor must be selected to withstand the converter to provide maximum currents and voltages with a safety factor around 50%. The n-type reinforcing MOSFET is better chosen for providing the safety factor, and the proposed converter design uses the same [35]. The diodes (D<sub>1</sub> and D<sub>2</sub>), and MOSFET switching losses and conduction losses were calculated and given in Equations (61)–(73).

Conduction losses of the diode D1 and D2:

$$P_{\rm D} = \int V_{\rm ak}(t) \, i_{\rm ak}(t) dt = V_{\rm D} i_{\rm ak+} R_{\rm D} I_{\rm akrms}^2 \tag{61}$$

$$R_{D1} = \left(\frac{p3}{2}p_{i} - V_{D1}I_{o}\right)\frac{(1-\delta)}{I_{o}^{2}}$$

(62)

$$R_{D1} = \left(\frac{p_3}{2}p_i - V_{D2}I_o\right)\frac{(1-\delta)}{I_o^2}$$

(63)

$$P_{D1} = V_{D1} i_{ak1+} R_{D1} I_{akrms1}^2$$

(64)

$$P_{D2} = V_{D2} i_{ak2+} R_{D2} I_{akrms2}^2$$

(65)

Switching losses of the Diode D<sub>1</sub> and D<sub>2</sub>:

$$P_{SD1} = \frac{t_{rr} - t_s}{T} V_{ak1} \dot{i}_{ak1}$$

(66)

$$P_{SD2} = \frac{t_{rr} - t_s}{T} V_{ak2} i_{ak2}$$

(67)

Conduction losses of the MOSFET:

$$P_{\text{MOSFET Conduction Loss}} = R_{\text{DS}_{\text{ON}}} i_{\text{MOSFET rms}}$$

(68)

$$i_{\text{MOSFET}} = \frac{2I_0}{(1-\delta)} \tag{69}$$

$$P_{P_{MOSFET switcing loss}} = \frac{t_{ON} + t_{OFF}}{T} (V_{MOS} i_{MOS}) + \frac{1}{2T} (C_{MOS} V_{MOS})^2$$

(13)

Total switching losses for the proposed converter is:

$$P_{\text{total switcing losses}} = \frac{t_{\text{ON}} + t_{\text{OFF}}}{T} (V_{\text{MOS}} i_{\text{MOS}}) + \frac{1}{2T} (C_{\text{MOS}} V_{\text{MOS}})^2 + 2 \frac{t_{\text{rr}-} t_s}{T} V_{ak} i_{ak}$$

(14)

$$t_{ON} = t_r(i_{MOS}) + t_f(V_{MOS})$$

(15)

$$t_{OFF} = t_f(i_{MOS}) + t_r(V_{MOS})$$

(16)

The efficiency of the proposed converter is found using

$$\eta = \left(\frac{p_{o}}{p_{i}}\right) = \frac{P_{i} - \sum P_{T}}{P_{i}}$$

(17)

where  $P_i$  = input power and  $\sum P_T$  = Total losses (P Diode2 Con.Losses + PDiode2 Con.Losses + PMOSFET switching loss + PMOSFET Conduction Loss).

#### 5. Simulation Results

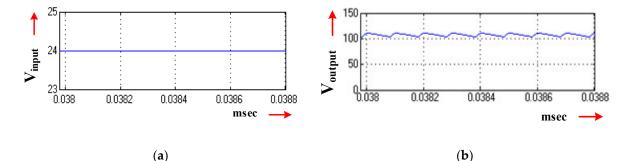

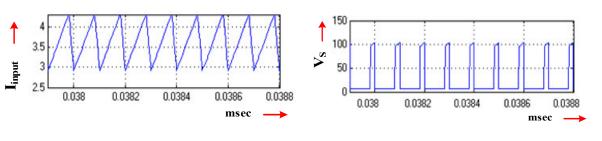

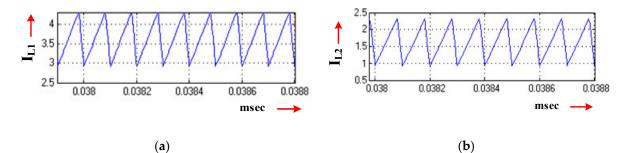

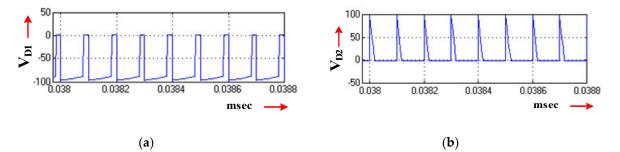

The hybrid DC-DC converter operation and performance estimation were modeled in the MATLAB/Simulink simulation platform and waveforms were presented. The simulation specification and parameter were as follows: The input power = 150 W, input voltage of the converter (V<sub>in</sub>) = 24 V, maximum duty cycle  $\delta$  = 0.8 and switching frequency f<sub>s</sub> = 10 kHz. The converter input and output inductors were  $L_1 = 1$  mH and  $L_2 = 1$  mH receptivity. The capacitors were  $C_1 = 100 \ \mu\text{F}$ ,  $C_2 = 100 \ \mu\text{F}$  and  $C_3 = 2 \ \mu\text{F}$ . Figures 14–17 show the proposed converter simulation results for 10 kHz switching frequency and 80% duty cycle, and the results confirm the theoretical values. The converter duty cycle was fixed to be equal to or less than 0.8 to minimize the conduction losses. From Figure 14, when the converter duty cycle was fixed at 0.8 with 24V input voltage, the converter delivered an output voltage of 124 V (5.166 times higher than the input voltage). During the continuous conduction mode, the inductance L1 current was limited within the saturation limit in the range of 3 to 4.5 A and maintained the converter input current. Figure 15 displays the input current, as well as voltage across the power switches, and Figure 17 shows  $D_1$  and  $D_2$  voltages,  $V_{D1}$ and  $V_{D2}$ , respectively, during the switching period. From the results, it could be seen that during the time of switching, the switches (MOSFET and diode) were maintained with their maximum allowable voltage as 100 V. It was verified that the voltage across the switches was less than that of the converter. From the  $i_{L2}$  and  $V_{D2}$  simulation results, it can be seen that the proposed converter maintains a continuous current capability. Figure 16 shows the simulation waveforms for the inductor current iL1 and inductor current iL2. From this waveform, it is seen that the inductors were charging uniformly and delivering the current in the continuous conduction. Figure 17 illustrates the voltage across the power diode,  $V_{D1}$  and  $V_{D2}$ . When the duty cycle was reduced to 0.6, the converter performance, switching reliability and continuous current capability were linear. Hence, the proposed converter has a wide range of controllability with a controlled degree of freedom to avail wider voltage outputs. The simulation was also performed in transient conditions (changing load and sudden change in the duty cycle). During this transient period, the output voltage and current through ill changed with a small transient period and after reaching the continuous conduction and maintaining the constant output voltage.

**Figure 14.** Simulation waveforms for input voltage 24V DC and 0.8 duty cycle; (**a**) input voltage waveform (voltage scale: 1 V/div and t: 20  $\mu$ s/div) and (**b**) input voltage waveform (voltage scale 50 V/div and t: 20  $\mu$ s/div).

(a)

(b)

**Figure 15.** Simulation waveforms for input voltage 24V DC and 0.8 duty cycle; (**a**) input current waveform (current scale: 0.5 A/div and t: 20  $\mu$ s/div) and (**b**) voltage across the power switch waveform (voltage scale 50 V/div and t: 20  $\mu$ s/div).

**Figure 16.** Simulation waveforms for input voltage 24 V DC and 0.8 duty cycle; (**a**) inductor current  $i_{L1}$  waveform (current scale: 0.5 A/div and t: 20 µs/div) and (**b**) inductor current  $i_{L2}$  waveform (current scale: 0.5 A V/div and t: 20 µs/div).

**Figure 17.** Simulation waveforms for input voltage 24V DC and 0.8 duty cycle; (**a**) voltage across the power diode, V<sub>D1</sub> waveform (voltage scale: 50 V/div and t: 20  $\mu$ s/div) and (**b**) voltage across the power diode, V<sub>D2</sub> waveform (voltage scale: 50 V/div and t: 20  $\mu$ s/div).

Figure 18. Voltage gain comparison of boost and Cuk with the proposed converter.

The proposed single switch hybrid DC–DC converter is compared with conventional converters (boost and Cuk) for different duty cycles from the range zero to one. The switching frequency and other circuit components for this evaluation were taken as being the same as the proposed converter values are given in the design (see Table 1). As expected, the proposed converter voltage gain was more than the boost and Cuk converter duty cycle. Figure 18 shows the voltage gain comparison of boost and Cuk with the proposed converter.

## 6. Experimental Results

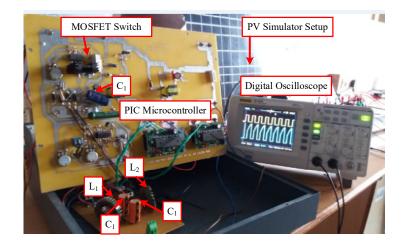

To confirm the experimental performance of the proposed hybrid DC–DC converter, the experimental laboratory setup was developed in collaboration with a Peripheral Interface Controller (PIC) microcontroller, as shown in Figure 19. To verify the theoretical and simulation results, the experimentations were conducted with similar values considered in the simulation studies. The converter was a 150 W circuit with parameters as listed in Table 1.

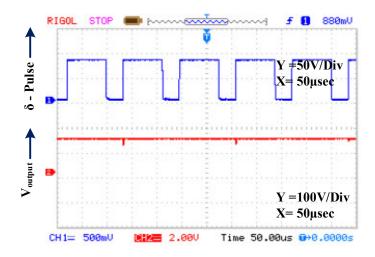

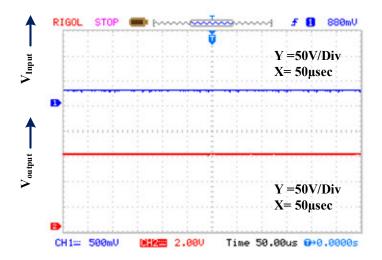

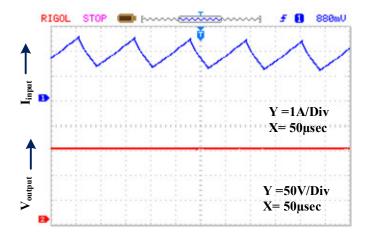

Similar to the simulation verification, the converter duty cycle was fixed as equal to or less than 0.8 to minimize the conduction losses. While testing the converter, the input DC source was fixed to generate constant input voltage and power as 24 V and 150 W range. As seen in Figure 20, while the converter duty cycle was fixed as 0.8, the corresponding output voltage was observed to be 122 V (closer to the simulation results). Figure 21 shows the converter input current and output voltage.

Figure 19. Prototype setup of the proposed converter.

| Components                                                            | Parameter               |  |  |

|-----------------------------------------------------------------------|-------------------------|--|--|

| Input power <i>P</i> <sub>input</sub>                                 | 150 W                   |  |  |

| Input voltage V <sub>in</sub>                                         | 24 V                    |  |  |

| Output power Po                                                       | 112 W                   |  |  |

| Switching frequency <i>f</i> <sup>s</sup>                             | 10 KHz                  |  |  |

| Power MOSFET                                                          | SiHB30N60E              |  |  |

| Diode $D_1$ and $D_2$                                                 | VS-15EWX06FN-M3         |  |  |

| Inductance $L_1$ and $L_2$                                            | 1 mH                    |  |  |

| Capacitor $C_1, C_2$ and $C_3$                                        | 100 μF, 100 μF and 2 μF |  |  |

| The output of Diode <i>V</i> <sub>D1</sub> and <i>V</i> <sub>D2</sub> | 100 V and 95 V          |  |  |

| Output Capacitor Vc1, Vc2 and Vc3                                     | 104 V, 110 V and 8 V    |  |  |

Table 1. Parameter of components of the proposed converter.

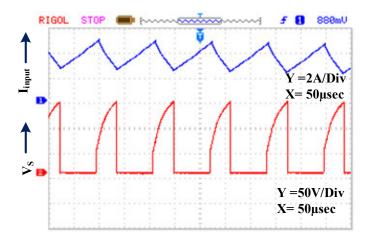

During the DC-to-DC conversion period, the converter maintained the continuous conduction with the inductance  $L_1$  current saturation limit range of 3 to 4.5 A, as depicted in Figure 22. Hence, the power switch was secured against the high rising current by maintaining the converter input current inductance  $L_1$  current saturation limit, which ensures the converter reliability against the

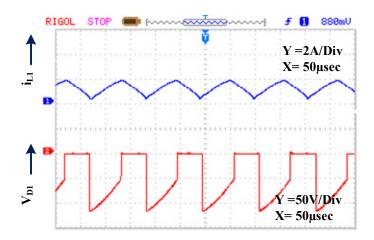

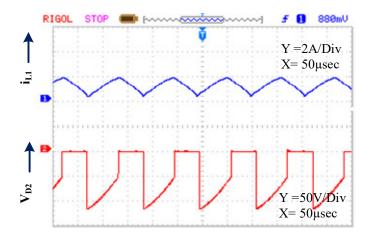

input source. Similarly, from Figures 23 and 24, during the time of switching, the MOSFET and diode were maintained with their maximum allowable voltage as 100 V, which was smaller than the converter output voltage (102 V). Here, during the switching period, the voltage across the main power switch was 100 V, and diode  $D_1$  and  $D_2$  were equal to  $V_{D1} = 100$  V and  $V_{D2} = 95$  V, respectively. During the entire mode of operation, the inductor current iL1 and iL2 maintained the identical current profile, which maintains the voltage balance between  $C_1$  and  $C_2$ . Figure 25 shows the experimental waveform of the input inductor current, *i*L1 and voltage across *i*D2 the power switch for input voltage 24 V and 0.8 duty cycle.

Next, the converter was operated by changing the duty ratio to observe transient operation behaviour. For the period of transient operation, the converter load was kept constant as the previous value. During the trial, the switching duty-cycle varied from 0.8 to 0.5. During this period, likely the output voltage decreased and stabilized after a few milliseconds. A similar response happened in the inductor current i*L*<sup>1</sup> and preserved in the converter in continuous conduction.

Figure 20. The experimental waveform of the duty cycle and input voltage.

**Figure 21.** The experimental waveform of input voltage and output voltage for input voltage 24 V and 0.8 duty cycle.

**Figure 22.** The experimental waveform of input current and output voltage for input voltage 24 V and 0.8 duty cycle.

**Figure 23.** The experimental waveform of input current and voltage across the power switch for input voltage 24 V and 0.8 duty cycle.

**Figure 24.** The experimental waveform of the input inductor current, *i*<sub>L1</sub> and voltage across *i*<sub>D1</sub> the power switch for input voltage 24 V and 0.8 duty cycle.

**Figure 25.** The experimental waveform of the input inductor current, *i*<sub>L1</sub> and voltage across *i*<sub>D2</sub> the power switch for input voltage 24 V and 0.8 duty cycle.

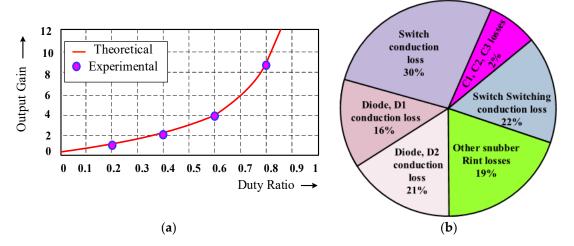

To validate the comparison of the theoretical and experimental results, the converter continuous conduction mode(CCM) state voltage gain was plotted concerning the variation duty ratio from 0.2 to 0.8 (see Figure 26a). From the results, it can be seen that the experimental values are very close to the theoretical calculations. Finally, the efficiency of the proposed converter was found under full load. The calculated experimental maximum efficiency of the proposed converter at 0.8 duty cycle is 92.2%. The calculated experimental maximum efficiency of the proposed converter is 92.2%. Figure 26b shows experimental power loss distribution operating at the rated condition. During duty ratio  $\delta = 0.8$ , the semiconductors ( $D_1$ ,  $D_2$  and MOSFET) switching losses were calculated as 0.4 W, 0.5 W and 1.2 W using equations (61)–(74). Hence, the total switching losses for the converter was 2.1 W. Similarly, the conduction of the power switches and other circuit parameters losses were observed. In the overall power distribution losses, the MOSFET switching loss and conduction loss alone are about 52%. As presented in Figure 26b, the I<sup>2</sup>R losses in the MOSFET, diode and the snubber circuitry losses were accounted for as significant losses. Nevertheless, the proposed converter voltage stress reduction helps to choose the lower voltage-rating switch, and hence conduction losses are expected to reduce.

**Figure 26.** (a) Theoretical and experimental results comparison. (b) Experimental power loss distribution operating at rated condition (duty ratio from 0.8).

#### Key Performance Comparison

For validating the proposed converter performance, Table 2 shows the comparison with other similar converters. According to the table, the proposed converter provides a better voltage gain with a single active switch, and normalized voltages stress of semiconductor devices is less when

compared to other converters. Based on the presented analysis and discussions, results and comparisons confirm the functionality and advantages of the proposed converter.

| Similar<br>Converter<br>Topology              | Converter<br>[39]                                           | Converter [9]                        | Converter<br>[30]        | Converter<br>]40]                          | Converter<br>[36]                | Proposed<br>Converter                      |

|-----------------------------------------------|-------------------------------------------------------------|--------------------------------------|--------------------------|--------------------------------------------|----------------------------------|--------------------------------------------|

| Switches used                                 | 1                                                           | 2                                    | 1                        | 1                                          | 1                                | 1                                          |

| Diodes used                                   | 5                                                           | 2                                    | 2                        | 3                                          | 1                                | 2                                          |

| No. of<br>Inductors used                      | 3                                                           | 2                                    | 2                        | 3                                          | 2                                | 2                                          |

| No. of<br>capacitors used                     | 3                                                           | 2                                    | 3                        | 3                                          | 3                                | 3                                          |

| Continuous<br>input current                   | Yes                                                         | No                                   | Yes                      | Yes                                        | No                               | Yes                                        |

| Voltage gain,<br>Vo                           | $\frac{\left(\delta\right)^2}{\left(1-\delta\right)^2}$ Vin | $\frac{2(1+\delta)}{(1-\delta)}$ Vin | $\frac{1}{1-\delta}$ Vin | $rac{\delta}{\left(1-\delta ight)^2}$ Vin | $\frac{2\delta}{(1-\delta)}$ Vin | $V_{O} = \frac{1+\delta}{1-\delta} V_{PV}$ |

| Efficiency                                    | 91%                                                         | 90%                                  | 91%                      | 90%                                        | 92%                              | 92.2%                                      |

| The voltage<br>stress on the<br>active switch | Moderate                                                    | Less                                 | High                     | Less                                       | High                             | Moderate                                   |

Table 2. Performance comparison of similar converter topology.

# 7. Conclusions

The high voltage gains and highly efficient single switch hybrid non-isolated DC–DC converter is shown in this paper. The proposed topology was derived by integrating conventional boost and Cuk converters. This topology produced a non-inverting output in continuous input current mode with a single switch having high voltage gain ( $\approx$ 5.116 gain). When compared with the classical boost and Cuk converters, the proposed topology facilitates a substantial voltage gain with comparable lower switching stress. The steady-state analysis under the CCM condition and design calculation for the proposed hybrid was discussed in detail.

Finally, the validation test done with the proposed converter privileges, the voltage gain, power switch voltage stress and elements used in the circuit simulation studies were presented. Characterize the proposed topology for its obtained performances, PIC microcontroller based real-time experimental setup was realized under the power rating of 150 W with an efficiency of 92.2%. Experimental results confirmed the practicability in real-time applications needs.

**Author Contributions:** All authors are involved in developing the concept, simulation and experimental validation and in proof-reading the article. All authors have read and agreed to the published version of the manuscript.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- 1. Mansouri, N.; Lashab, A.; Sera, D.; Guerrero, J.M.; Cherif, A. Large Photovoltaic Power Plants Integration: A Review of Challenges and Solutions. *Energies* **2019**, *12*, 3798.

- 2. Deng, F.; Chen, Z. Control of improved full-bridge three-level DC/DC converter for wind turbines in a DC grid. *IEEE Trans. Power Electron.* **2013**, *28*, 314–324.

- Mangu, B.; Akshatha, S.; Suryanarayana, D.; Fernandes, B.G. Grid-Connected PV-Wind-Battery-Based Multi-Input Transformer-Coupled Bidirectional DC-DC Converter for Household Applications. *IEEE J. Emerg. Sel. Top. Power Electron.* 2016, 4, 1086–1095.

- 4. Chiu, H.J.; Yao, C.J.; Lo, Y.K. A DC-DC converter topology for renewable energy systems. *Int. J. Circuit Theory Appl.* **2009**, *37*, 485–495.

- 6. Hu, X.; Gong, C. A High Gain Input-Parallel Output-Series DC/DC Converter With Dual Coupled Inductors. *IEEE Trans. Power Electron.* **2015**, *30*, 1306–1317.

- 7. Kouro, S.; Leon, J.I.; Vinnikov, D.; Franquelo, L.G. Grid-Connected Photovoltaic Systems: An Overview of Recent Research and Emerging PV Converter Technology. *IEEE Ind. Electron. Mag.* **2015**, *9*, 47–61.

- Khooban, M.H.; Gheisarnejad, M.; Farsizadeh, H.; Masoudian, A.; Boudjadar, J. A New Intelligent Hybrid Control Approach for DC–DC Converters in Zero-Emission Ferry Ships. *IEEE Trans. Power Electron.* 2020, 35, 5832–5841.

- Farsizadeh, H.; Gheisarnejad, M.; Mosayebi, M.; Rafiei, M.; Khooban, M.H. An Intelligent and Fast Controller for DC/DC Converter Feeding CPL in a DC Microgrid. *IEEE Trans. Circuits Syst. II Express Br.* 2020, (early access).

- 10. Sarrafan, N.; Zarei, J.; Razavi-Far, R.; Saif, M. Khooban, M.H. A Novel On-Board DC/DC Converter Controller Feeding Uncertain Constant Power Loads. *IEEE J. Emerg. Sel. Top. Power Electron.* **2020**, (early access).

- Chen, Y.; Zhao, S.; Li, Z.; Wei, X. Kang, Y. Modelling and Control of the Isolated DC–DC Modular Multilevel Converter for Electric Ship Medium Voltage Direct Current Power System. *IEEE J. Emerg. Sel. Top. Power Electron.* 2017, *5*, 124–139.

- 12. Amjadi, Z.; Williamson, S.S. Power-electronics-based solutions for plug-in hybrid electric vehicle energy storage and management systems. *IEEE Trans. Ind. Electron.* **2010**, *57*, 608–616.

- Boico, F.; Lehman, B.; Shujaee, K. Solar battery chargers for NiMH batteries. *IEEE Trans. Power Electron.* 2007, 22, 1600–1609.

- Chen, S.J.; Yang, S.P.; Huang, C.M.; Chou, H.M.; Shen, M.J. Interleaved High Step-Up DC-DC Converter Based on Voltage Multiplier Cell and Voltage-Stacking Techniques for Renewable Energy Applications. *Energies* 2018, 11, 1632.

- 15. Hsieh, Y.P.; Chen, J.F.; Liang, T.J.; Yang, L.S. Novel high step-up DC-DC converter for distributed generation system. *IEEE Trans. Ind. Electron.* **2013**, *60*, 1473–1482.

- 16. Todorovic, M.H.; Palma, L.; Enjeti, P.N. Design of a wide input range dc–dc converter with a robust power control scheme suitable for fuel cell power conversion. *IEEE Trans. Ind. Electron.* **2008**, *55*, 1247–1255.

- Wai, R.J.; Lin, C.Y.; Lin, C.Y.; Duan, R.Y.; Chang, Y.R. High efficiency power conversion system for kilowatt-level stand-alone generation unit with low input voltage. *IEEE Trans. Ind. Electron.* 2008, 55, 3702– 3714.

- 18. Changchien, S.K.; Liang, T.J.; Chen, J.F.; Yang, L.S. Novel high stepup dc-dc converter for fuel cell energy conversion system. *IEEE Trans. Ind. Electron.* **2010**, *57*, 2007–2017.

- 19. Chen, S.; Liang, T.; Yang, L.; Chen, J. A cascaded high step-up dc–dc converter with single switch for micro source applications. *IEEE Trans. Power Electron*. **2011**, *26*, 1146–1153.

- 20. Vighetti, S.; Ferrieux, J.-P.; Lembeye, Y. Optimization and design of a cascaded DC/DC converter devoted to grid-connected photovoltaic systems. *IEEE Trans. Power Electron.* **2012**, *27*, 2018–2027.

- 21. Pan, C.T.; Lai, C.M. A high-efficiency high step-up converter with low switch voltage stress for fuel-cell system applications. *IEEE Trans. Ind. Electron.* **2010**, *57*, 1998–2006.

- 22. Grant, D.A.; Darroman, Y.; Suter, J. Synthesis of tapped-inductor switched-mode converters. *IEEE Trans. Power Electron*. **2007**, *22*, 1964–1969.

- 23. Wai, R.J.; Lin, C.Y.; Duan, R.Y.; Chang, Y.R. High-efficiency DC–DC converter with high voltage gain and reduced switch stress. *IEEE Trans. Ind. Electron.* **2007**, *54*, 354–364.

- 24. Wu, T.F.; Lai, Y.S.; Hung, J.C.; Chen, Y.M. Boost converter with coupled inductors and buck-boost type of active clamp. *IEEE Trans. Ind. Electron.* **2008**, *55*, 154–162.

- 25. Wijeratne, D.S.; Moschopoulos, G. Quadratic power conversion for power electronics: Principles and circuits. *IEEE Trans. Circ. Syst.* 2012, *59*, 426–438.

- Kadri, R.; Gaubert, J.P.; Champenois, G.; Mostefaï, M. Performance analysis of transformer less single switch quadratic Boost converter for grid connected photovoltaic systems. In Proceedings of the International Conference on Electrical Machines, Rome, Italy, 6–8 September 2010; pp. 1–7.

- 27. Liang, T.J.; Tseng, K.C. Analysis of integrated boost-flyback step up converter. *IEEE Proc. Electr. Power Appl.* **2005**, *152*, 217–225.

- 28. Fretias. A.; Tofoli, F.L.; Jbbunior, E.M.S.; Daher, S.; Antunes, F.L.M. High-voltage gain DC-DC boost converter with coupled inductors for photovoltaic systems. *IET Power Electron.* **2015**, *8*, 1885–1892.

- 29. Khalilzadeh, M.; Abbaszadeh, K.; Non-isolated high step-up DC-DC converter based on coupled inductor with reduced voltage stress. *IET Power Electron*. **2015**, *8*, 2184–2194.

- Saravanan, S.; Ramesh Babu, N. Analysis and implementation of high step-up DC-DC converter for PV based grid application. *Appl. Energy* 2017, 190, 64–72.

- 31. Wu, G.; Ruan, X.; Ye, Z. Non isolated high step-up DC-DC converters adopting switched-capacitor cell. *IEEE Trans. Ind. Electron.* **2015**, *62*, 383–393.

- 32. Poorali, B.; Torkan, A.; Adib, E. High step-up Z-source DC-DC converter with coupled inductors and switched capacitor cell. *IET Power Electron*. **2015**, *8*, 1394–1402.

- 33. Zhao, Y.; Li, W.; He, X. Single-phase improved active clamp coupled-inductor based converter with extended voltage doubler cell. *IEEE Power Electron*. **2012**, *27*, 2869–2878.

- Yang, L.S.; Liang, T.J.; Lee, H.C.; Chen, J.F. Novel high step-up DC-DC converter with coupled-inductor and voltage-doubler circuits. *IEEE Trans. Ind. Electron.* 2011, 58, 4196–4206.

- 35. Bharatiraja, C.; Sanjeevikumar, P.; Mahesh, Swathimala, A.S.; Raghu, S. Analysis, design and investigation on a new single-phase switched quasi Z-source inverter for photovoltaic application. *Int. J. Power Electron. Drive Syst.* **2017**, *8*, 853–860.

- 36. Banaei, M.R.; Ardi, H.; Farakhor, A. Analysis and implementation of a new single-switch buck-boost DC/DC converter. *IET Power Electron*. **2014**, *7*, 1906–1914.

- Banaei, M.R.; Bonab, H.A.F. A Novel Structure for Single-Switch Non isolated Transformerless Buck-Boost DC-DC Converter. *IEEE Trans. Ind. Electron.* 2017, 64, 198–205.

- Banaei, M.R.; Sani, S.G. Analysis and Implementation of a New SEPIC-Based Single-Switch Buck-Boost DC-DC Converter With Continuous Input Current. *IEEE Trans. Power Electron.* 2018, 33, 10317–10325.

- 39. Zhang, N.; Zhang, G.; See, K.W.; Zhang, B. A Single-Switch Quadratic Buck–Boost Converter With Continuous Input Port Current and Continuous Output Port Current. *IEEE Trans. Power Electron.* **2018**, *33*, 4157–4166.

- Maroti, P.K.; Padmanaban, S.; Wheeler, P.; Blaabjerg, F.; Rivera, M. Modified high voltage conversion inverting cuk DC-DC converter for renewable energy application. In Proceedings of the IEEE Southern Power Electronics Conference (SPEC) 2017, Puerto Varas, Chile, 4–7 December 2017; pp. 1–5.

- Oluwafemi, A.W.; Ozsoy, E.; Padmanaban, S.; Bhaskar, M.S.; Ramachandaramurthy, V.K.; Fedák, V. A modified high output-gain cuk converter circuit configuration for renewable applications—A comprehensive investigation. In Proceedings of the IEEE Conference on Energy Conversion (CENCON) 2017, Kuala Lumpur, Malaysia, 30–31 October 2017; pp. 117–122.

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).